### **Energy-scalable Speech Recognition Circuits**

by

### Michael Price

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2016

© Massachusetts Institute of Technology 2016. All rights reserved.

Certified by ..... Anantha Chandrakasan Vannevar Bush Professor of Electrical Engineering and Computer Science Thesis Supervisor

Certified by .....

James Glass Senior Research Scientist Thesis Supervisor

Accepted by ...... Professor Leslie A. Kolodziejski Chair, Department Committee on Graduate Students

#### **Energy-scalable Speech Recognition Circuits**

by

#### Michael Price

Submitted to the Department of Electrical Engineering and Computer Science on May 19, 2016, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

As people become more comfortable with speaking to machines, the applications of speech interfaces will diversify and include a wider range of devices, such as wearables, appliances, and robots. Automatic speech recognition (ASR) is a key component of these interfaces that is computationally intensive. This thesis shows how we designed special-purpose integrated circuits to bring local ASR capabilities to electronic devices with a small size and power footprint.

This thesis adopts a holistic, system-driven approach to ASR hardware design. We identify external memory bandwidth as the main driver in system power consumption and select algorithms and architectures to minimize it. We evaluate three acoustic modeling approaches–Gaussian mixture models (GMMs), subspace GMMs (SGMMs), and deep neural networks (DNNs)–and identify tradeoffs between memory bandwidth and recognition accuracy. DNNs offer the best tradeoffs for our application; we describe a SIMD DNN architecture using parameter quantization and sparse weight matrices to save bandwidth. We also present a hidden Markov model (HMM) search architecture using a weighted finite-state transducer (WFST) representation. Enhancements to the search architecture, including WFST compression and caching, predictive beam width control, and a word lattice, reduce memory bandwidth to 10 MB/s or less, despite having just 414 kB of on-chip SRAM. The resulting system runs in real-time with accuracy comparable to a software recognizer using the same models. We provide infrastructure for deploying recognizers trained with open-source tools (Kaldi) on the hardware platform.

We investigate voice activity detection (VAD) as a wake-up mechanism and conclude that an accurate and robust algorithm is necessary to minimize system power, even if it results in larger area and power for the VAD itself. We design fixed-point digital implementations of three VAD algorithms and explore their performance on two synthetic tasks with SNRs from -5 to 30 dB. The best algorithm uses modulation frequency features with an NN classifier, requiring just 8.9 kB of parameters.

Throughout this work we emphasize energy scalability, or the ability to save energy when high accuracy or complex models are not required. Our architecture exploits scalability from many sources: model hyperparameters, runtime parameters such as beam width, and voltage/frequency scaling. We demonstrate these concepts with results from five ASR tasks, with vocabularies ranging from 11 words to 145,000 words.

Thesis Supervisor: Anantha Chandrakasan Title: Vannevar Bush Professor of Electrical Engineering and Computer Science

Thesis Supervisor: James Glass Title: Senior Research Scientist

### Acknowledgments

All of the acknowledgments in my Master's thesis<sup>1</sup> remain valid with equal weight.

Thanks to my sponsors for making this research possible. My first year was supported by a Joan and Irwin Jacobs fellowship. The remainder of the work was sponsored by Quanta Computer Inc. as part of the Qmulus Project. Terence Huang, Joe Polifroni, Jamey Hicks, Rongquen Chen, and Ted Chang were very supportive of the work and offered insight on the use cases for our technology. The company provided extreme hospitality on our two trips to their headquarters in Taiwan, which were rare opportunities for someone who had never left North America. TSMC provided access to their 65 nm process technology and libraries, and fabricated our chip designs through their University Shuttle Program. Synopsys, Cadence, and Mentor Graphics provided the EDA tools used to design and verify these chips; Xilinx provided FPGA boards and synthesis tools for prototyping. Thanks also to the corporate members of the Center for Integrated Circuits and Systems (CICS), who are always engaging at the biannual reviews, and probably paid for part of this research somehow.

Anantha Chandrakasan was the first to invite me back to MIT and the prime motivator of this work. He allowed me to choose from a wide variety of research topics and granted broad freedom in my day-to-day work, which is the primary reason I went to graduate school. He has a strong vision for each of his many research efforts and high (perhaps unrealistic, but well-intentioned) expectations for his students to follow. Working with Anantha has provided a window into the life of a highly successful and globally respected leader–probably the hardest working person that I know.

Jim Glass has been a statesman and a role model as a research advisor. He agreed to collaborate with Anantha and myself in the unfamiliar and caveat-rich world of hardware. He would meet with me every week, discussing the technical roadblocks that we needed to overcome or preparing for interactions with our sponsors. He helped drive me towards higher application performance (e.g., accuracy), making our circuit contributions more valuable. And he organized events, from reading groups to backyard barbecues, that perpetuated a sense of community.

Victor Zue brought patience and wisdom as a member of the thesis committee, helping me present the work effectively for the long term. He provided a steady stream of high-quality pastries and tea leaves for the graduate students, which were a pleasant surprise (even as someone who has become desensitized to free food). He also arranged the productive collaboration between MIT and Quanta, of which this research was a small part.

<sup>&</sup>lt;sup>1</sup>Please see http://hdl.handle.net/1721.1/52771.

Vladimir Stojanovic was an ideal graduate counselor, having supervised my Master's thesis work and recommended that I pursue graduate school (which I belatedly accepted). Peter Hagelstein offered considerate advice and moving stories from his colorful career. Vivienne Sze served on my RQE committee and offered occasional advice on research and career choices. Najim Dehak taught me a lot about audio classification and provided frequent entertainment, even audible from long distances.

The support staff at MIT make students' lives easier and also more entertaining. Margaret Flaherty and Marcia Davidson were both highly effective and professional administrators, in their own unique ways. Mike McIIrath has a difficult yet crucial job as MTL's foundry liason and CAD software administrator. Mike Hobbs and Bill Maloney (MTL) and Scott Cyphers, Steve Ruggiero, Jonathan Proulx, and Garrett Wollman (CSAIL) assisted with compute and network infrastructure.

It's been a pleasure working with my fellow students in Anantha's group and the SLS group. As a parttime member of both groups, I was able to participate in all of the parties but avoid any responsibilities. I'm fortunate to consider you friends as well as coworkers. Frank Yaul has been a polymath and inspiration, always ready to discuss anything from inference algorithms to PCB designs, or escape to rock climbing or ice skating. Dave Harwath, Ekapol Chuangsuwanich, and Stephen Shum helped with designing and understanding speech algorithms, and also convinced me to drink beer. Mehul Tikekar, Priyanka Raina, Chiraag Juvekar, and Arun Paidimarri helped with the difficult difficulties of digital circuit design. My research program was fairly self-contained (isolated), making it especially rewarding to collaborate with Bonnie Lam, Xinkun Nie, Skanda Koppula, Mandy Korpusik, Eann Tuan, Patricia Saylor, and Sumit Dutta on their projects. Many others, including my office mates Ann, Xue, Yonatan and Jen, and lab mates Phil and Nachiket, made my days more interesting. I won't truly celebrate until all of you have graduated.

Other people at MIT who have rounded out my career (i.e., provided excellent distractions from research) include Ed Moriarty of the Edgerton Center, and Ken Stone and Hayami Arakawa of the Hobby Shop. (My apologies for deserting them, as I have "graduated" to my own household electronics and woodworking facility.)

My wife Michelle has surprised me with her continued love, and provided a world apart from the noise and confusion of daily life that I can retreat to.

To everyone acknowledged here, I offer my appreciation and a permanent invitation to meet again.

## Contents

### Glossary

### 18

| 1 | Intro | oductio  | n                                                           | 23 |

|---|-------|----------|-------------------------------------------------------------|----|

|   | 1.1   | Motiva   | tion                                                        | 23 |

|   | 1.2   | Scope    |                                                             | 24 |

|   | 1.3   | ASR fo   | ormulation                                                  | 26 |

|   | 1.4   | Prior a  | rt                                                          | 30 |

|   | 1.5   | Contri   | butions                                                     | 31 |

|   | 1.6   | Guide    | to chapters                                                 | 32 |

| 2 | Aco   | ustic mo | odeling                                                     | 33 |

|   | 2.1   | What i   | s the most accurate acoustic model with 1 MB of parameters? | 34 |

|   |       | 2.1.1    | Gaussian mixture model (GMM)                                |    |

|   |       | 2.1.2    | Subspace Gaussian mixture model (SGMM)                      | 37 |

|   |       | 2.1.3    | Deep neural network (DNN)                                   | 39 |

|   |       | 2.1.4    | Model comparison and discussion                             | 41 |

|   | 2.2   | Neural   | network implementation                                      | 43 |

|   |       | 2.2.1    | Architecture and general tradeoffs                          | 43 |

|   |       | 2.2.2    | Scalability                                                 | 45 |

|   |       | 2.2.3    | Sequencer and EU design                                     | 46 |

|   |       | 2.2.4    | Sigmoid                                                     | 49 |

|   | 2.3   | Summ     | ary                                                         | 52 |

| 3 | Sear  | ch       |                                                             | 53 |

|   | 3.1   | Archite  | ecture                                                      | 54 |

|   |       |          |                                                             |    |

|   | 3.2  | Building blocks                                       | 57  |

|---|------|-------------------------------------------------------|-----|

|   |      | 3.2.1 Hash table                                      | 57  |

|   |      | 3.2.2 State list                                      | 59  |

|   |      | 3.2.3 WFST                                            | 60  |

|   |      | 3.2.4 Beam width control                              | 67  |

|   |      | 3.2.5 Word lattice                                    | 69  |

|   | 3.3  | Interactions                                          | 75  |

|   | 3.4  | Performance and scalability                           | 75  |

|   | 3.5  | Summary                                               | 78  |

| 4 | Voic | e activity detection                                  | 79  |

|   | 4.1  | Accuracy influences power consumption                 | 79  |

|   | 4.2  | Algorithms                                            | 80  |

|   |      | 4.2.1 Energy-based (EB)                               | 80  |

|   |      | 4.2.2 Harmonicity (HM)                                | 82  |

|   |      | 4.2.3 Modulation frequencies (MF)                     | 82  |

|   | 4.3  | Architecture                                          | 85  |

|   |      | 4.3.1 Top level                                       | 85  |

|   |      | 4.3.2 Energy-based (EB)                               | 86  |

|   |      | 4.3.3 Harmonicity (HM)                                | 87  |

|   |      | 4.3.4 Modulation frequencies (MF)                     | 88  |

|   | 4.4  | Performance comparisons                               | 89  |

|   | 4.5  | Summary                                               | 92  |

| 5 | Infr | astructure                                            | 93  |

|   | 5.1  | Circuits                                              | 93  |

|   |      | 5.1.1 Front-end                                       | 93  |

|   |      | 5.1.2 ASR control                                     | 95  |

|   |      | 5.1.3 Supervisory logic                               | 96  |

|   | 5.2  | Design tools                                          | 99  |

|   |      | 5.2.1 Binary-backed data structures                   | 99  |

|   |      | 5.2.2 Unit testing with hardware/software equivalence | 100 |

|   | 5.3  | Software                                              | 102 |

|   |      | 5.3.1      | Kaldi modifications                 | . 102 |

|---|------|------------|-------------------------------------|-------|

|   |      | 5.3.2      | Model suite preparation             | . 103 |

|   | 5.4  | Summ       | ary                                 | . 104 |

| 6 | IC I | mpleme     | entation                            | 105   |

|   | 6.1  | Overvi     | iew                                 | . 105 |

|   | 6.2  | Synthe     | esis flow information               | . 105 |

|   |      | 6.2.1      | Clock gating: explicit and implicit | . 109 |

|   |      | 6.2.2      | Floorplan                           | . 110 |

|   |      | 6.2.3      | Timing considerations               | . 111 |

|   | 6.3  | Test se    | etup                                | . 113 |

|   |      | 6.3.1      | РСВ                                 | . 114 |

|   |      | 6.3.2      | FPGA                                | . 115 |

|   |      | 6.3.3      | Software                            | . 116 |

|   | 6.4  | Result     | s                                   | . 117 |

|   |      | 6.4.1      | Voltage/frequency scaling           | . 118 |

|   |      | 6.4.2      | ASR power consumption               | . 119 |

|   |      | 6.4.3      | ASR subsystem efficiency            | . 121 |

|   |      | 6.4.4      | Explicit clock gating               | . 123 |

|   |      | 6.4.5      | VAD                                 | . 124 |

|   | 6.5  | Summ       | ary                                 | . 126 |

| - | Car  |            |                                     | 107   |

| 7 |      | Conclusion |                                     | 127   |

|   | 7.1  | Summ       | nary                                | . 127 |

|   |      | 7.1.1      | Contributions                       | . 127 |

|   |      | 7.1.2      | Performance and scalability         | . 129 |

|   | 7.2  | Future     | e work                              | . 129 |

|   |      | 7.2.1      | Design and application refinement   | . 130 |

|   |      | 7.2.2      | System integration                  | . 132 |

|   |      | 7.2.3      | Leveraging technological change     | . 133 |

## **List of Figures**

| 1-1 | Power gated speech recognizer concept. The scope of the work includes the software and        |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | circuit components within the dashed boxes                                                    | 25 |

| 1-2 | Progression of research program through three IC tapeouts.                                    | 27 |

| 1-3 | HMM formulation of ASR. Separate frameworks are used to evaluate the transition proba-        |    |

|     | bilities $p(x_{t+1} x_t)$ (bottom) and observation probabilities $p(y_t x_t)$ (right).        | 28 |

| 2-1 | Signal processing steps used to extract mel-frequency cepstral coefficients (MFCCs)           | 33 |

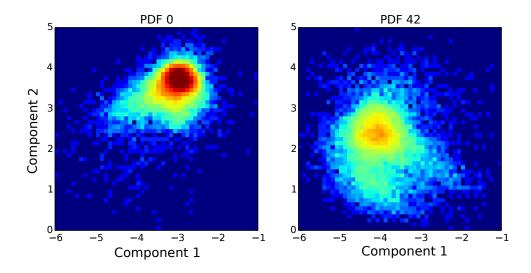

| 2-2 | Heat map of MFCCs within two tied states, taken from 894 WSJ utterances and projected to      |    |

|     | 2 dimensions using principal components analysis (PCA)                                        | 34 |

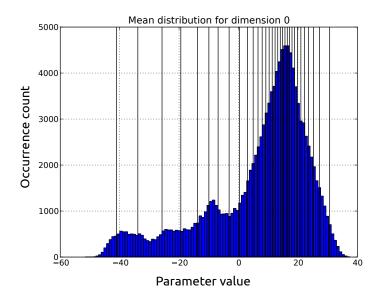

| 2-3 | Minimum distortion quantizer bins (black vertical lines) follow the empirical distribution of |    |

|     | the parameters the quantizer is used to compress (in this example, GMM means for the first    |    |

|     | dimension of the feature space).                                                              | 36 |

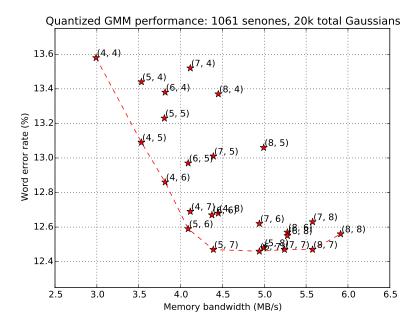

| 2-4 | GMM bandwidth and accuracy with independently varied quantization bit depths for (means,      |    |

|     | variances). Nominal ASR accuracy can be achieved with 5–7 bits                                | 37 |

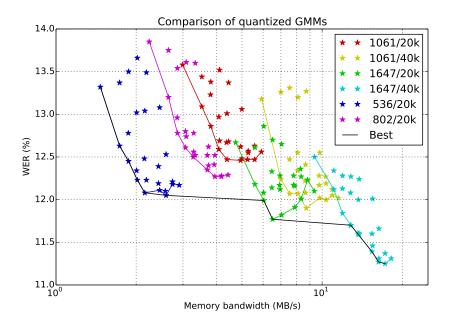

| 2-5 | Bandwidth/accuracy tradeoff for GMM acoustic model. Each color represents a model size        |    |

|     | (number of tied states and total number of Gaussian components), as shown in the legend.      |    |

|     | The stars plotted in each color represent different combinations of mean and variance quan-   |    |

|     | tization depth                                                                                | 38 |

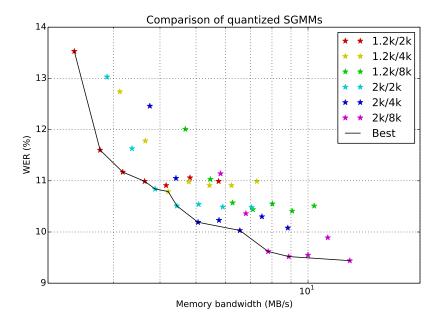

| 2-6 | Bandwidth/accuracy tradeoff for SGMM acoustic model. Each color represents a model            |    |

|     | size (number of tied states and total number of substates), as shown in the legend. The stars |    |

|     | plotted in each color represent different quantization depths applied to all parameters       | 39 |

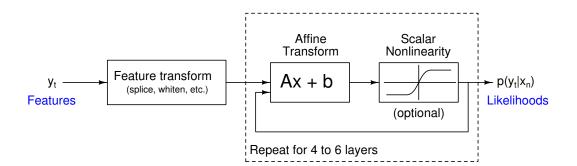

| 2-7 | Schematic of NN evaluation.                                                                   | 40 |

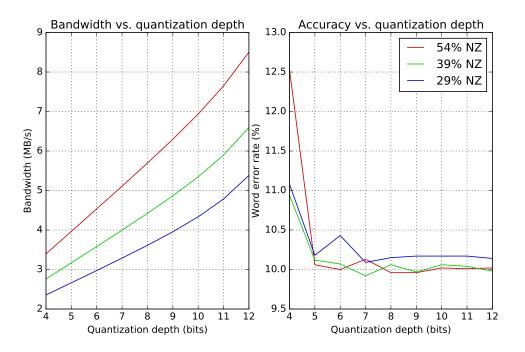

| 2-8 | Bandwidth (left) and accuracy (right) of 512-node, 6-layer NN acoustic models trained with    |    |

|     | different fractions of nonzero (NZ) weights.                                                  | 42 |

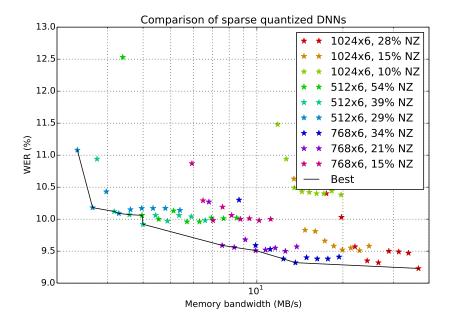

| 2-9  | Bandwidth/accuracy tradeoffs across many NN acoustic models. The dimensions and weight             |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | matrix sparsity of each model are shown in the legend.                                             | 42 |

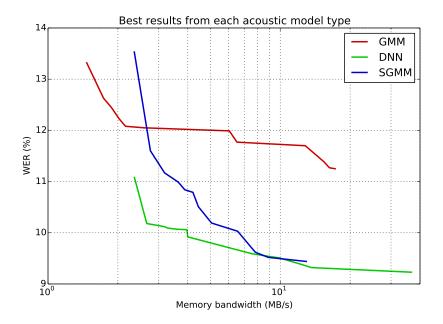

| 2-10 | Bandwidth/accuracy comparison of acoustic model frameworks, using the best results from            |    |

|      | each framework                                                                                     | 43 |

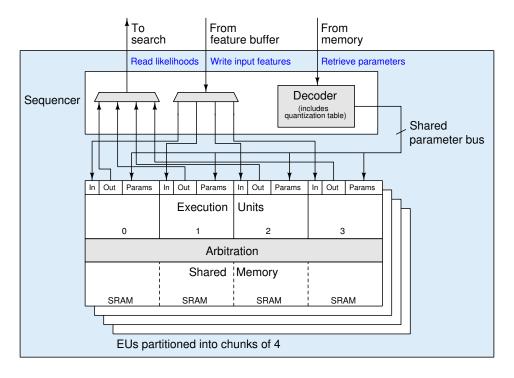

| 2-11 | Block diagram of SIMD NN evaluator, relying on a shared sequencer and 32 execution units.          | 44 |

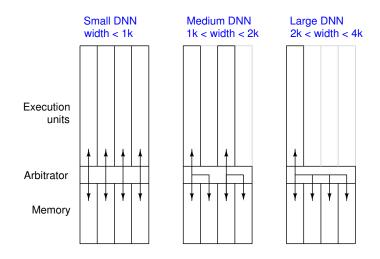

| 2-12 | Execution units and local memory are grouped into chunks that can be reconfigured for              |    |

|      | different network sizes                                                                            | 45 |

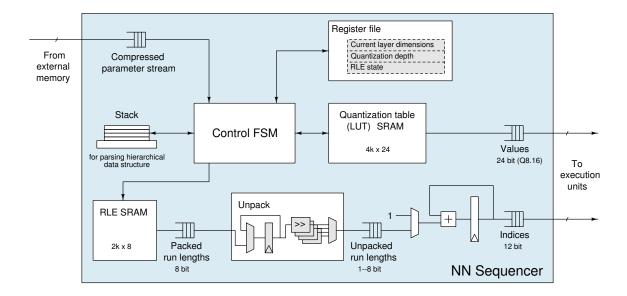

| 2-13 | NN sequencer architecture supporting sparse and quantized weight matrices                          | 47 |

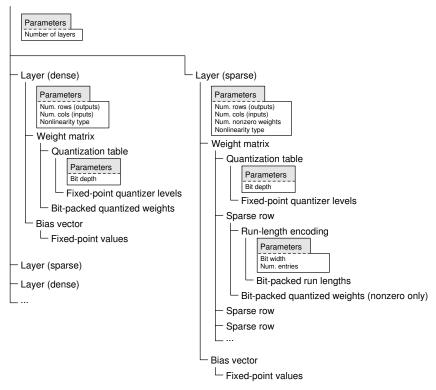

| 2-14 | Compressed neural network data structure. Each layer is stored in either sparse or dense           |    |

|      | format (whichever uses fewer bytes)                                                                | 48 |

| 2-15 | Variable-width run length encoding is used to represent the column indices of nonzeros             |    |

|      | within each row of a sparse weight matrix.                                                         | 48 |

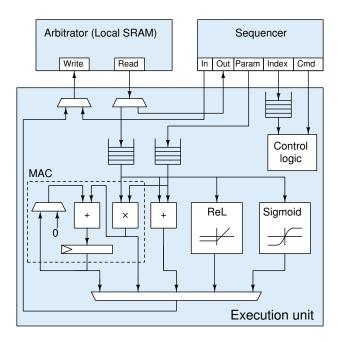

| 2-16 | Execution unit block diagram (pipelining, addresses, and control signals not shown)                | 49 |

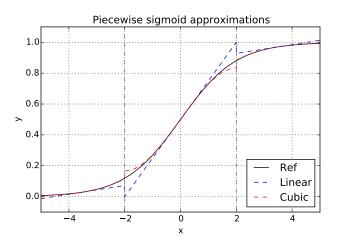

| 2-17 | The sigmoid function and simple piecewise polynomial fits                                          | 50 |

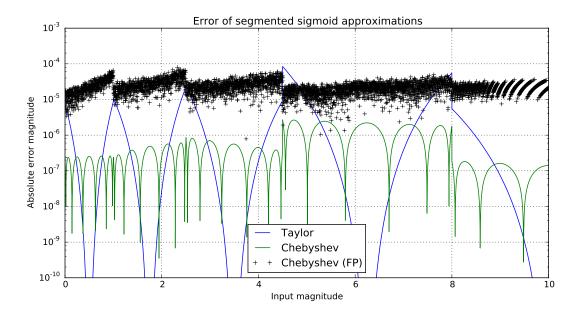

| 2-18 | Approximation error of piecewise polynomial fits to sigmoid function, comparing Taylor             |    |

|      | and Chebyshev series                                                                               | 51 |

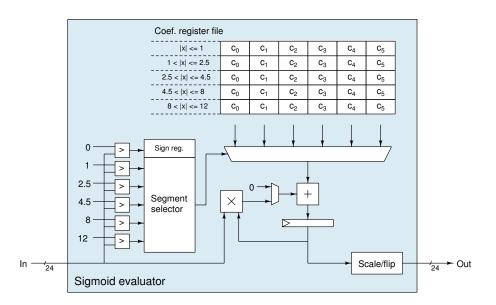

| 2-19 | Block diagram of piecewise polynomial sigmoid evaluator.                                           | 51 |

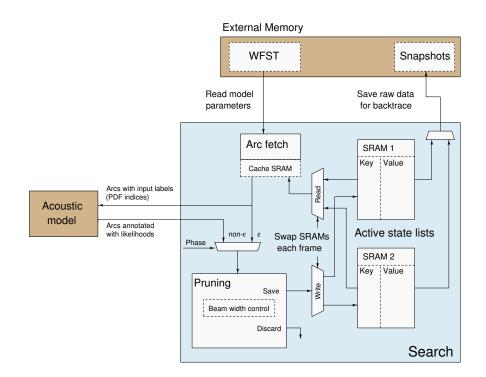

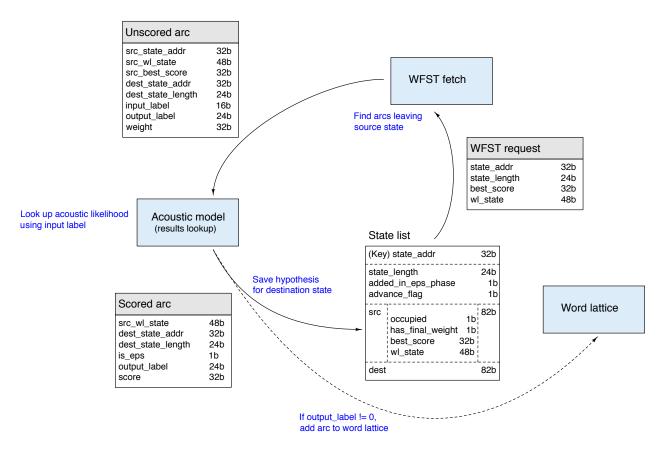

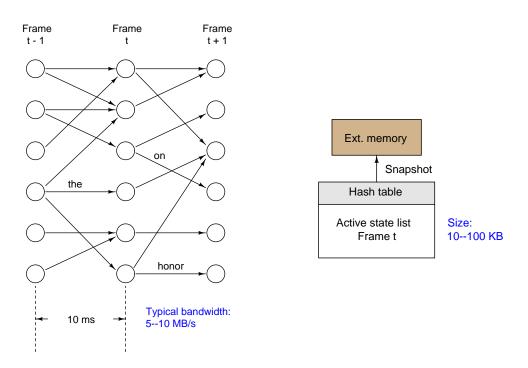

| 3-1  | Baseline search architecture with two-frame state list memory.                                     | 54 |

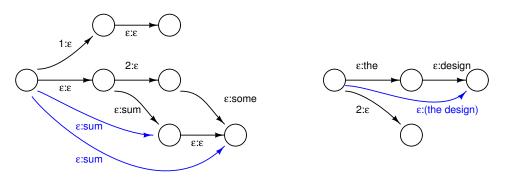

| 3-2  | WFST preprocessing with multi-word output symbols. Left: Adding $\epsilon$ arcs to bypass arbi-    |    |

|      | trary length chains of only $\epsilon$ arcs [16]. Right: Compound word labels are created for arcs |    |

|      | that by<br>pass multiple non- $\epsilon$ output labels                                             | 55 |

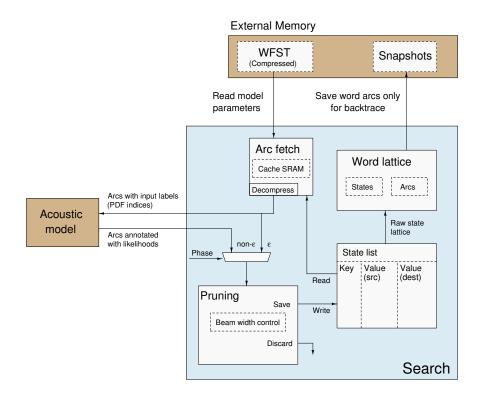

| 3-3  | Improved search architecture including word lattice and merged state lists                         | 56 |

| 3-4  | Data storage format for SRAM-based hash table with open addressing. Linear probing is              |    |

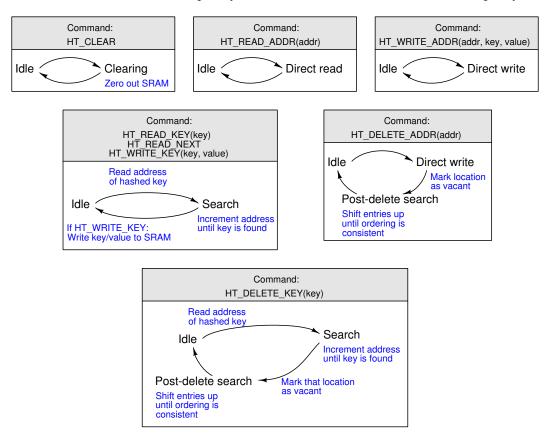

|      | used to resolve collisions.                                                                        | 57 |

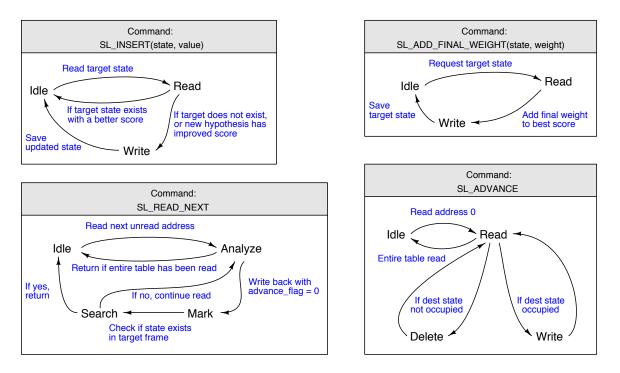

| 3-5  | State transition diagrams for SRAM-based hash table. (Resizing is performed as needed in           |    |

|      | between commands, using the same basic operations.)                                                | 58 |

| 3-6  | Data fields for state list entries and in-flight hypotheses. The architecture is designed to       |    |

|      | preserve memory locality.                                                                          | 60 |

| 3-7  | Guide to common state list operations, building on functionality provided by the hash table        | 61 |

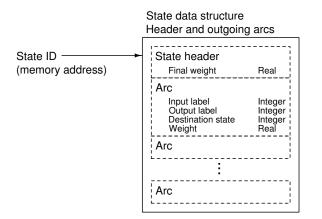

| 3-8  | WFST data structure: a key/value store where keys are state IDs, and values contain all            |    |

|      | outgoing arcs from each state.                                                                     | 62 |

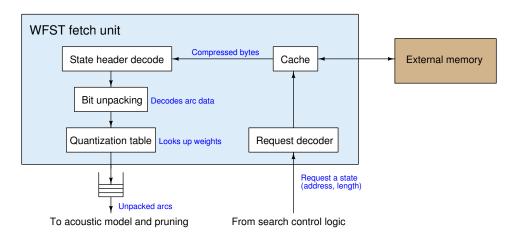

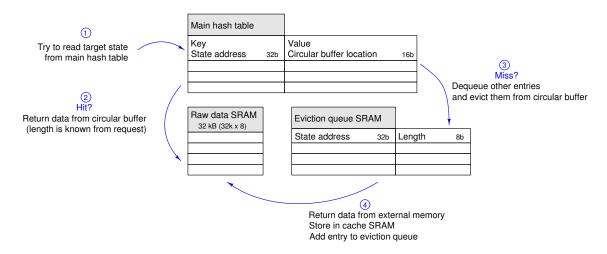

| 3-9  | WFST fetch architecture with caching and model compression                                  | 62       |

|------|---------------------------------------------------------------------------------------------|----------|

| 3-10 | WFST cache architecture, including eviction queue and hash table so that variable-length    |          |

|      | objects can be stored in a circular buffer                                                  | 63       |

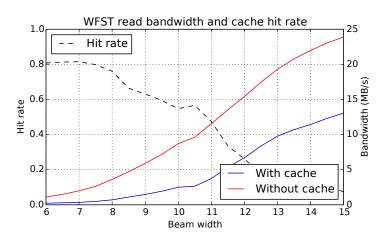

| 3-11 | WFST cache performance with varying beam width. A wider beam increases the working          |          |

|      | set size.                                                                                   | 64       |

| 3-12 | WFST cache performance can be optimized by setting a maximum cacheable state length         |          |

|      | which depends on the task and beam width.                                                   | 65       |

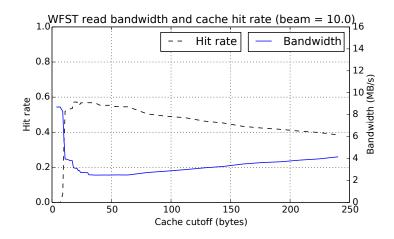

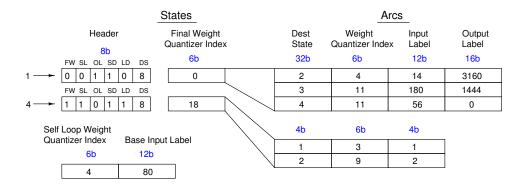

| 3-13 | Example WFST, along with the OpenFST representation (totaling 832 bits) for states 1 and 4. | 66       |

| 3-14 | Compressed format (272 bits) for the states in Figure 3-13. An 8-bit header configures the  |          |

|      | storage format for each state                                                               | 66       |

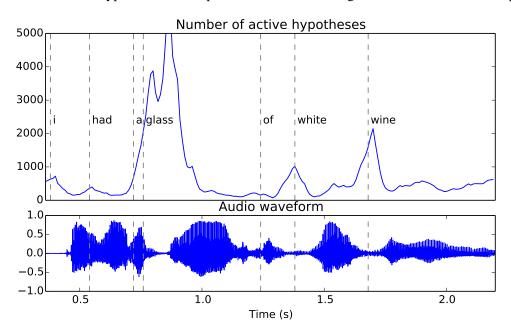

| 3-15 | The changing level of ambiguity in the speech signal causes search workload to vary over    |          |

|      | time                                                                                        | 67       |

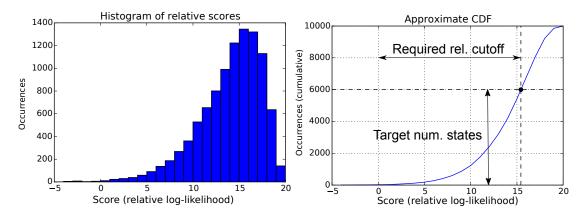

| 3-16 | A histogram of relative log-likelihoods (left) is used to approximate the CDF (right) and   |          |

|      | predict an appropriate beam width for the desired state cutoff                              | 69       |

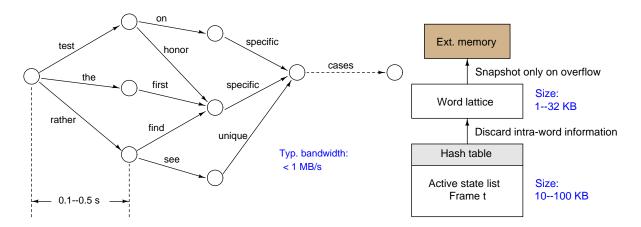

| 3-17 | State lattice generated during decoding (left); state snapshot concept (right)              | 70       |

| 3-18 | Word lattice example (left); word lattice snapshot concept (right)                          | 70       |

| 3-19 | Data structures used in word lattice.                                                       | 71       |

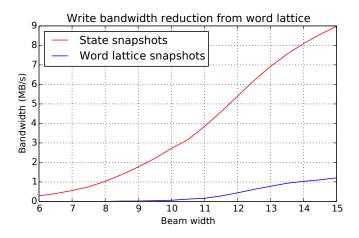

| 3-20 | Write bandwidth comparison of state lattice and word lattice approaches. Time-averaged      |          |

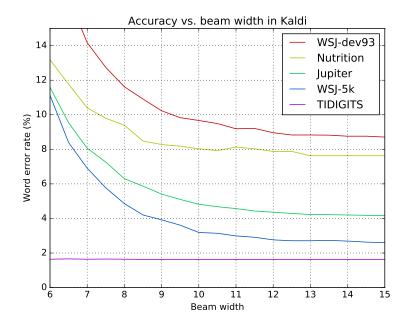

|      | bandwidth was measured on one of the harder utterances in the nutrition test set            | 75       |

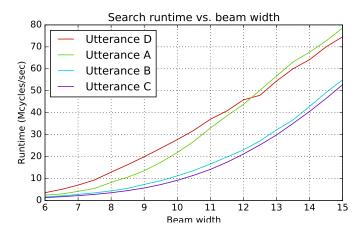

| 3-21 | WER vs. beam width for each ASR task, evaluated in Kaldi.                                   | 76       |

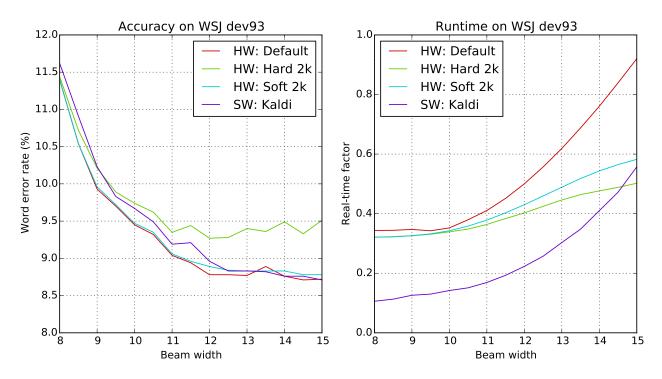

| 3-22 | Runtime scales with beam width and varies between utterances.                               | 77       |

| 3-23 | WER (left) and RTF (right) for search using varying soft and hard cutoffs, compared to      |          |

|      | Kaldi. (Hardware recognizer is run at 80 MHz.)                                              | 78       |

| 4 1  |                                                                                             |          |

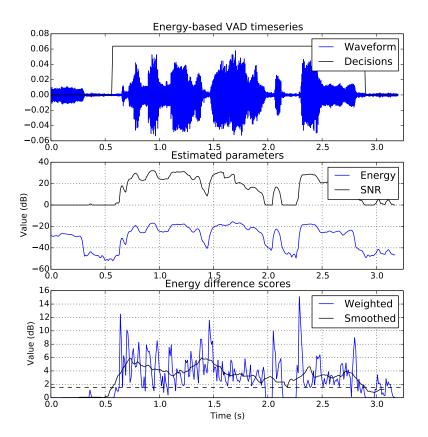

| 4-1  | Energy-based VAD operation including waveform (top), estimated frame-level energy and       | 01       |

| 4.0  |                                                                                             |          |

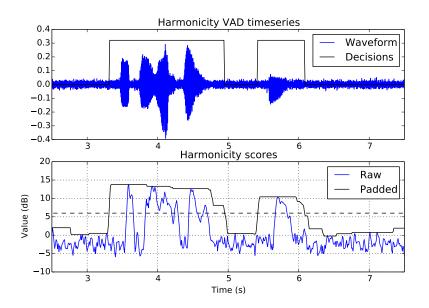

| 4-2  |                                                                                             | 83       |

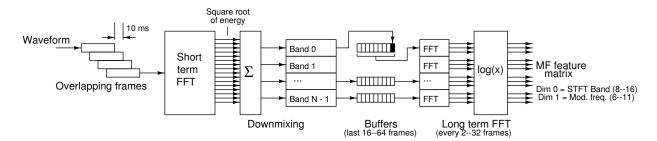

| 4-3  | Modulation frequency (MF) feature extraction. The use of both short-term and long-term      | 0.0      |

|      | FFTs allows MF features to capture temporal patterns that are unique to speech.             | 83       |

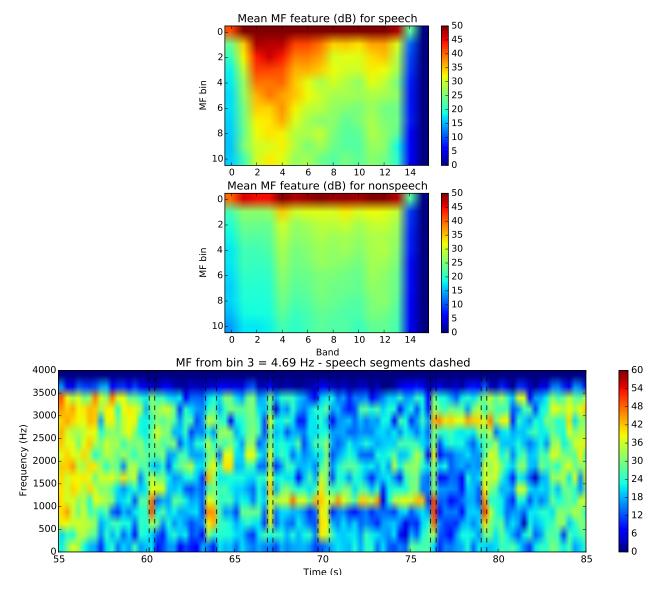

| 4-4  | Example of mean MF matrix for speech and non-speech (top), and 4 Hz MF spectra (bottom)     | <u> </u> |

|      |                                                                                             | 84       |

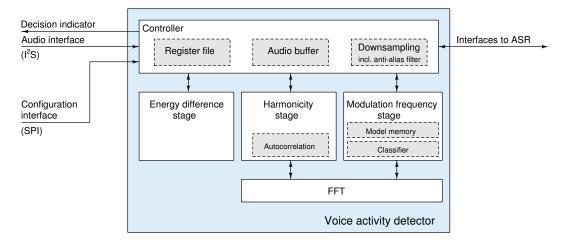

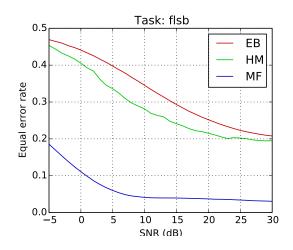

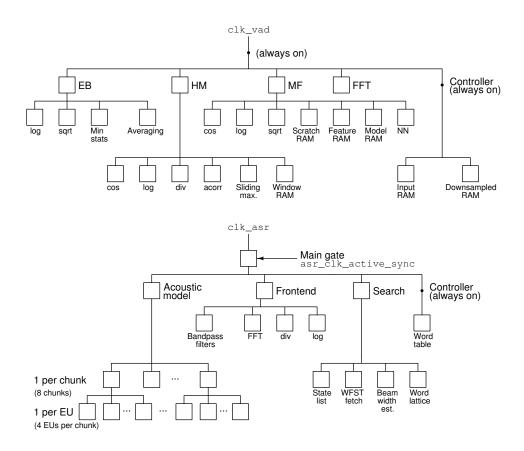

| 4-5  | Block diagram of VAD module that can selectively enable EB, HM, and MF algorithms           | 85       |

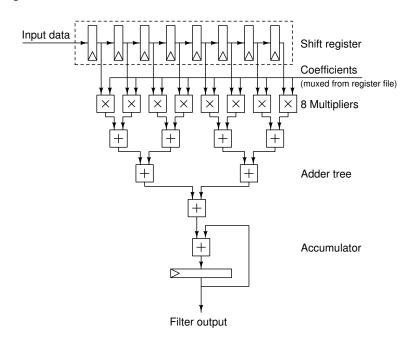

| 4-6  | The VAD provides a 65-tap antialiasing filter that evaluates 8 taps per cycle                                   | 86  |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

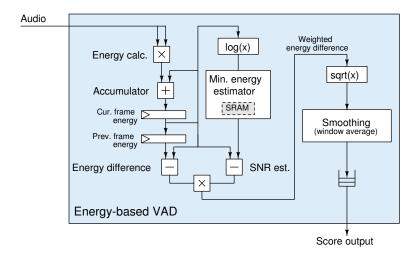

| 4-7  | Architecture of energy-based VAD module. This module evaluates the difference of energy                         |     |

|      | between two frames and weights it with an estimate of SNR                                                       | 87  |

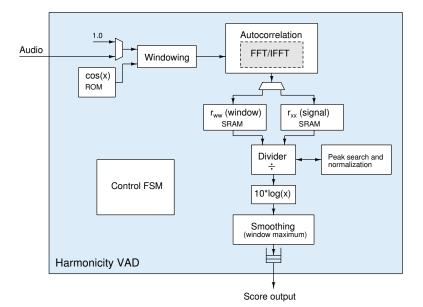

| 4-8  | Architecture of harmonicity VAD module. This module computes a normalized autocorre-                            |     |

|      | lation $\frac{r_{xx}}{r_{ww}}$ to obtain the amplitude ratio of periodic and non-periodic components, expressed |     |

|      | in dB as harmonicity.                                                                                           | 88  |

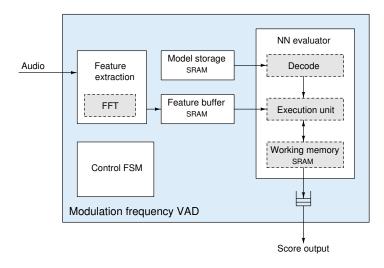

| 4-9  | Architecture of MF VAD module. This module performs modulation frequency feature                                |     |

|      | extraction and then classification. On-chip memory is used to store a small NN model for                        |     |

|      | classification.                                                                                                 | 89  |

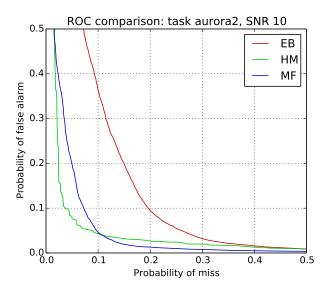

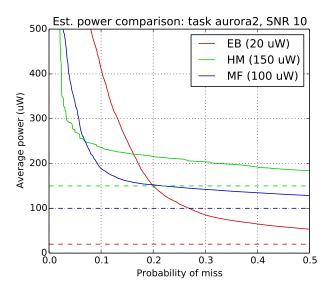

| 4-10 | Frame-level ROC of each VAD on Aurora2 task at 10 dB average SNR                                                | 90  |

| 4-11 | Estimated system power, derived from ROC of Figure 4-10, with 1 mW downstream power                             |     |

|      | and 5% speech duty cycle. VAD power figures are educated guesses                                                | 90  |

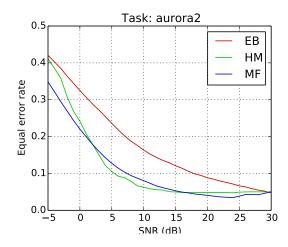

| 4-12 | EER vs. average SNR on Aurora2 task.                                                                            | 91  |

| 4-13 | EER vs. average SNR on Forklift/Switchboard task.                                                               | 91  |

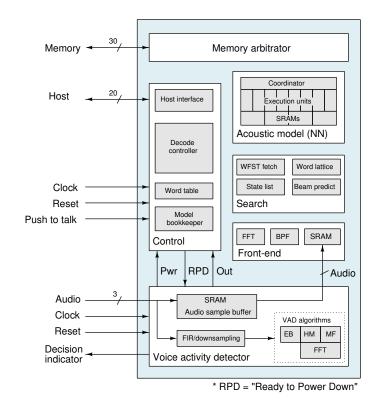

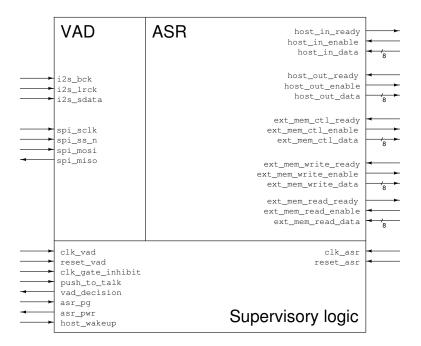

| 5-1  | Block diagram of the complete IC design, including top-level interfaces and internal ASR/VAD                    |     |

|      | interfaces                                                                                                      | 94  |

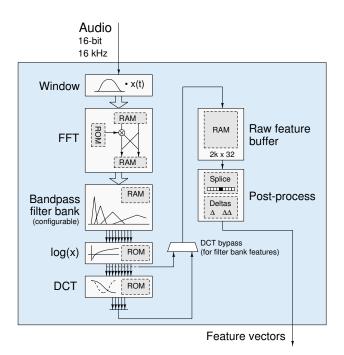

| 5-2  | Front-end block diagram. The frontend buffers raw features and applies output transforma-                       |     |

|      | tions on-the-fly to save memory.                                                                                | 95  |

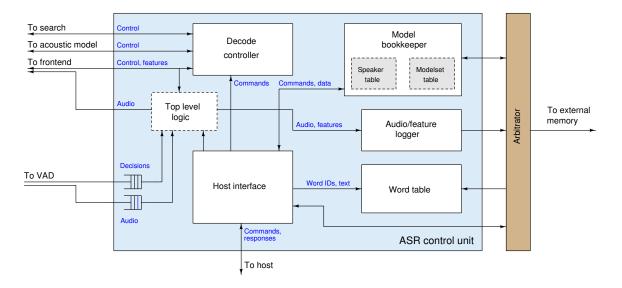

| 5-3  | Block diagram of ASR controller. The decode controller module coordinates the operation                         |     |

|      | of front-end, acoustic model, and search; interface responsibilities such as audio/feature                      |     |

|      | logging are delegated to other modules.                                                                         | 97  |

| 5-4  | State transition rules for supervisory logic controlling isolation, reset, clock, and power state               |     |

|      | of ASR                                                                                                          | 97  |

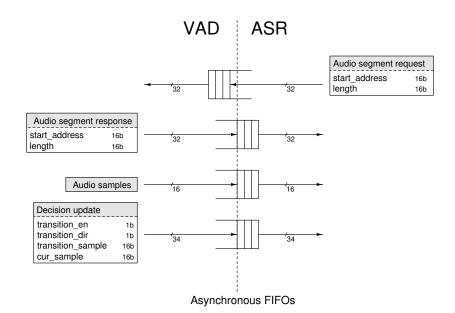

| 5-5  | VAD/ASR interfaces allow the ASR to retrieve earlier audio samples after it is woken up by                      |     |

|      | the VAD.                                                                                                        | 98  |

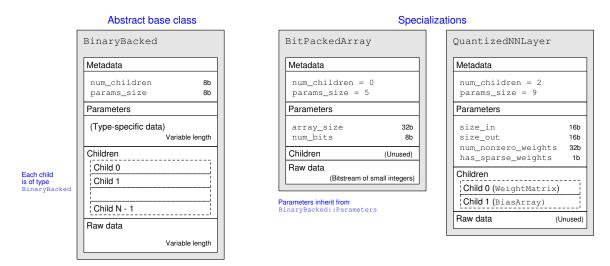

| 5-6  | Hierarchical binary-backed data structure: base class (left) and example implementations                        |     |

|      | (right)                                                                                                         | 99  |

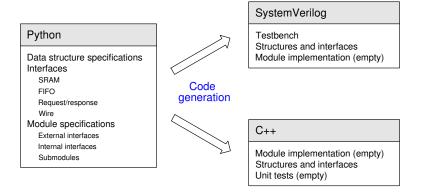

| 5-7  | Tools for generating simulation models with hardware/software equivalence                                       | 01  |

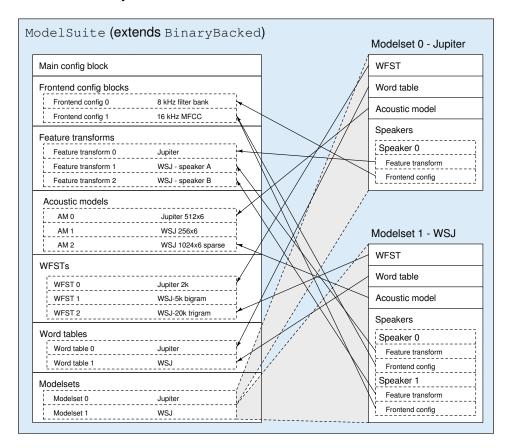

| 5-8  | The ModelSuite data structure allows multiple Kaldi recognizers to be compiled into                             |     |

|      | a single binary blob. This example shows a configuration supporting weather information                         |     |

|      | (Jupiter) and business news (WSJ) tasks                                                                         | .03 |

| 6-1  | Top level pinout partitioned into ASR, VAD, and supervisory regions                            |

|------|------------------------------------------------------------------------------------------------|

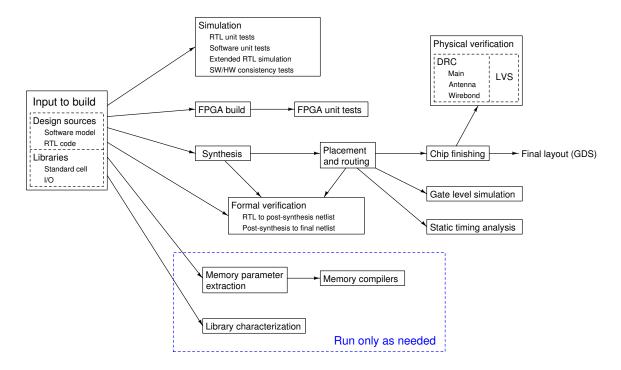

| 6-2  | Physical design flowchart illustrating the dependencies between different steps of IC imple-   |

|      | mentation                                                                                      |

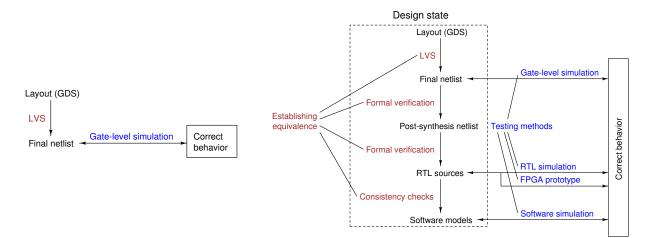

| 6-3  | Verification chains: ideal (left) and real (right)                                             |

| 6-4  | Clock gating hierarchy: VAD clock domain (top), ASR clock domain (bottom) 109                  |

| 6-5  | Interaction between voltage areas is designed so that voltage differences are consistent with  |

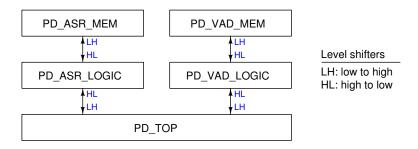

|      | level shifter orientation                                                                      |

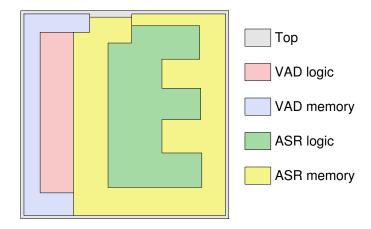

| 6-6  | The ASR/VAD chip floorplan groups logic into contiguous regions to simplify optimization       |

|      | by the placement and routing tool                                                              |

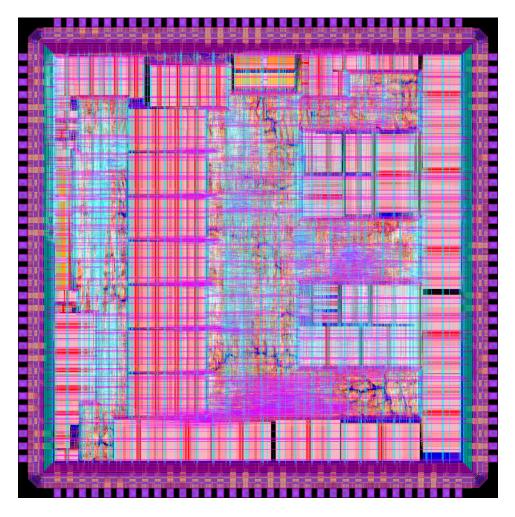

| 6-7  | ASR/VAD chip layout                                                                            |

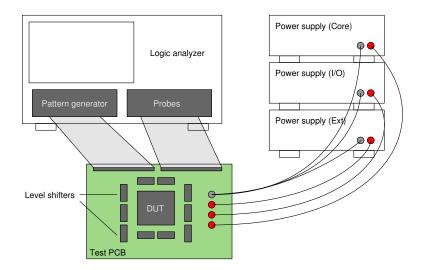

| 6-8  | A conventional digital IC test setup requires the coordination of several pieces of lab equip- |

|      | ment                                                                                           |

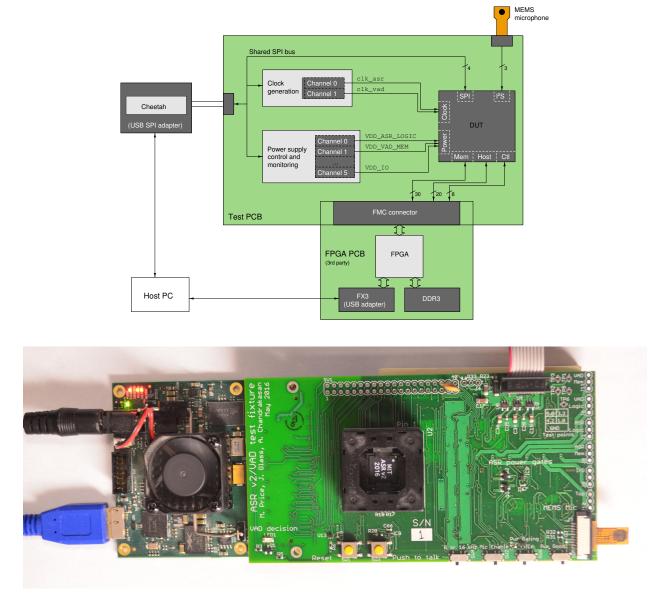

| 6-9  | Block diagram (top) and photo (bottom) of test PCB stack integrating power supplies and        |

|      | functional test interfaces                                                                     |

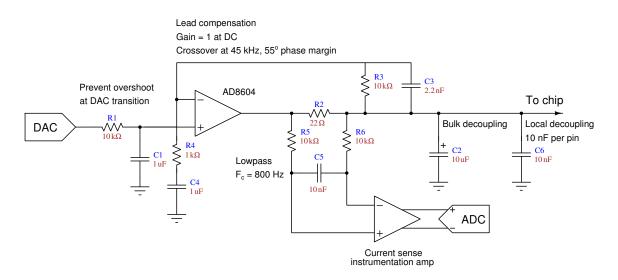

| 6-10 | Onboard programmable power supply regulator with current sense resistor inside the feed-       |

|      | back loop                                                                                      |

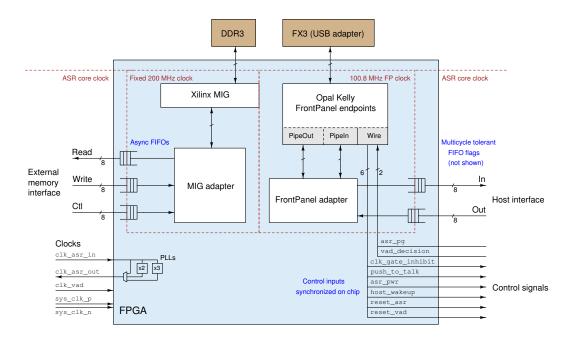

| 6-11 | FPGA-based adapter for generic host, memory, and control interfaces                            |

| 6-12 | Software modules used for ASR/VAD testing and demonstration                                    |

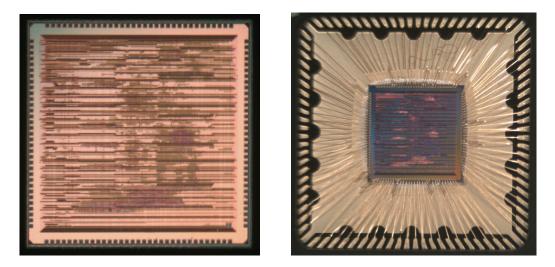

| 6-13 | ASR/VAD chip photos: bare die (left) and 88-pin QFN package (right).                           |

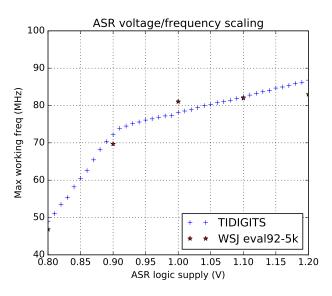

| 6-14 | Maximum working frequency for ASR as a function of logic supply voltage                        |

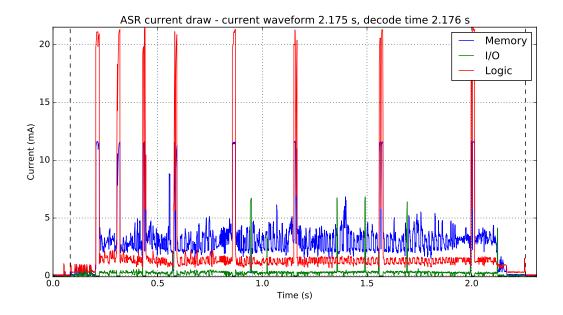

| 6-15 | Waveforms of selected power supply currents during ASR decoding                                |

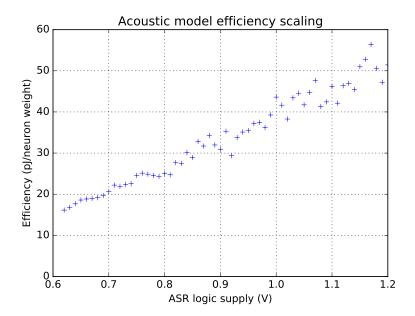

| 6-16 | Acoustic model efficiency varies by a factor of 3 due to voltage/frequency scaling 122         |

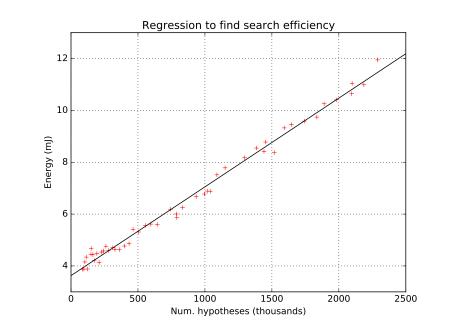

| 6-17 | Regression to estimate search efficiency from decoding results at different beam widths 123    |

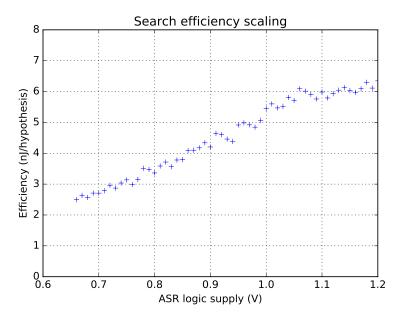

| 6-18 | Search efficiency scales quadratically with the memory supply voltage                          |

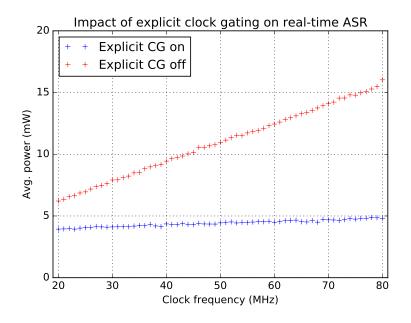

| 6-19 | Power consumption with and without explicit clock gating                                       |

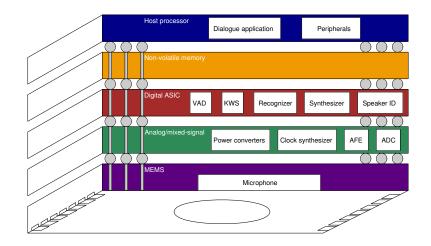

| 7-1  | Vision for single-chip speech processing solution                                              |

## **List of Tables**

| 1.1 | Datasets used for ASR experiments                                                              |

|-----|------------------------------------------------------------------------------------------------|

| 2.1 | Scalability owing to design of different NN acoustic models. Runtimes are quoted in clock      |

|     | cycles per second of utterance time                                                            |

| 3.1 | Compression ratios for <i>HCLG</i> WFST models                                                 |

| 3.2 | Algorithms used in word lattice generation                                                     |

| 3.3 | Search workload for each ASR task. Workload is specified in hypotheses, and runtime in         |

|     | clock cycles, per second of utterance time                                                     |

| 5.1 | Summary of host interface commands                                                             |

| 5.2 | Summary of host interface responses                                                            |

| 6.1 | Summary of ASR/VAD chip area                                                                   |

| 6.2 | Static timing verification scenarios covering the space of expected supply voltage combina-    |

|     | tions. "Nom" indicates the nominal $V_{DD}$ of the standard cell library and "Red" indicates a |

|     | reduced $V_{DD}$                                                                               |

| 6.3 | Timing optimization scenarios cover the extremes of possible multivoltage operating points.    |

|     | "Nom" refers to the nominal $V_{DD}$ of the standard cell library                              |

| 6.4 | ASR/VAD chip power supplies                                                                    |

| 6.5 | Power consumption averaged over each ASR task                                                  |

| 6.6 | Estimation of acoustic model efficiency over a single utterance                                |

| 6.7 | Initial measurements of VAD power consumption                                                  |

| 7.1 | ASR performance summary                                                                        |

| 7.2 | VAD performance summary                                                                        |

# Glossary

| ADC   | analog-to-digital converter                 |

|-------|---------------------------------------------|

| API   | application programming interface           |

| ASIC  | application-specific integrated circuit     |

| ASR   | automatic speech recognizer                 |

| BC    | best-case                                   |

| CDF   | cumulative distribution function            |

| CMOS  | complementary metal-oxide semiconductor     |

| CMVN  | cepstral mean and variance normalization    |

| CNN   | convolutional neural network                |

| DAC   | digital-to-analog converter                 |

| DDR   | double data rate                            |

| DNN   | deep neural network                         |

| DRAM  | dynamic random-access memory                |

| EB    | energy-based                                |

| EDA   | electronic design automation                |

| EER   | equal error rate                            |

| EU    | execution unit                              |

| FFT   | fast Fourier transform                      |

| FIFO  | first-in/first-out                          |

| FIR   | finite impulse response                     |

| fMLLR | feature-space maximum likelihood regression |

| FPGA  | field-programmable gate array               |

| fps   | frames per second                           |

| GDS   | Graphic Database System                     |

| GMM   | Gaussian mixture model                      |

| GPIB  | General Purpose Interface Bus               |

| HM    | harmonicity                                 |

| HMM   | hidden Markov model                         |

| HTK   | HMM Toolkit [91]                            |

| I <sup>2</sup> S                           | Inter-IC Sound                                                                                                                                                                            |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IC                                         | integrated circuit                                                                                                                                                                        |

| IEEE                                       | Institute of Electrical and Electronics Engineers                                                                                                                                         |

| IFFT                                       | inverse FFT                                                                                                                                                                               |

| IP                                         | intellectual property                                                                                                                                                                     |

| KWS                                        | keyword spotting                                                                                                                                                                          |

| KW3                                        | keyword spotting                                                                                                                                                                          |

| LDA                                        | linear discriminant analysis                                                                                                                                                              |

| LEF                                        | Library Exchange Format                                                                                                                                                                   |

| LM                                         | language model                                                                                                                                                                            |

| LRT                                        | likelihood ratio test                                                                                                                                                                     |

| LSTM                                       | long short-term memory                                                                                                                                                                    |

| LTFT                                       | long-term Fourier transform                                                                                                                                                               |

| LUT                                        | lookup table                                                                                                                                                                              |

| MAC                                        | multiply/accumulate                                                                                                                                                                       |

| MAP                                        | maximum a posteriori                                                                                                                                                                      |

| MEMS                                       | micro electromechanical system                                                                                                                                                            |

| MF                                         | modulation frequency                                                                                                                                                                      |

| MFCC                                       | mel-frequency cepstral coefficient                                                                                                                                                        |

| MIG                                        | Memory Interface Generator                                                                                                                                                                |

| MLC                                        | multilevel cell                                                                                                                                                                           |

| MMI                                        | maximum mutual information                                                                                                                                                                |

| NN                                         | neural network                                                                                                                                                                            |

| PC                                         | personal computer                                                                                                                                                                         |

| PCA                                        | principal components analysis                                                                                                                                                             |

| PCB                                        | printed circuit board                                                                                                                                                                     |

| QFN                                        | quad flat no-leads                                                                                                                                                                        |

| ReL                                        | rectified linear                                                                                                                                                                          |

| RLE                                        | run-length encoding                                                                                                                                                                       |

| RNN                                        | recurrent neural network                                                                                                                                                                  |

| ROC                                        | receiver operating characteristic                                                                                                                                                         |

| ROM                                        | read-only memory                                                                                                                                                                          |

| RTF                                        | real-time factor                                                                                                                                                                          |

| RTL                                        | register transfer level                                                                                                                                                                   |

| SGMM<br>SIMD<br>SLC<br>SNR<br>SPI<br>SPICE | subspace GMM<br>single instruction/multiple data<br>single-level cell<br>signal-to-noise ratio<br>Serial Peripheral Interface<br>Simulation Program with Integrated Circuit Em-<br>phasis |

| SRAM<br>STFT<br>STL<br>SV<br>SVD<br>SVD | static random-access memory<br>short-term Fourier transform<br>Standard Template Library<br>SystemVerilog<br>singular value decomposition<br>support vector machine |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TC                                      | typical-case                                                                                                                                                        |

| TDNN                                    | time-delay neural network                                                                                                                                           |

| TSMC                                    | Taiwan Semiconductor Manufacturing Company                                                                                                                          |

|                                         |                                                                                                                                                                     |

| UBM                                     | universal background model                                                                                                                                          |

| UPF                                     | Unified Power Format                                                                                                                                                |

| USB                                     | Universal Serial Bus                                                                                                                                                |

| UVM                                     | Universal Verification Methodology                                                                                                                                  |

| VAD                                     | voice activity detector                                                                                                                                             |

| WC                                      | worst-case                                                                                                                                                          |

| WER                                     | word error rate                                                                                                                                                     |

| WFST                                    | weighted finite-state transducer                                                                                                                                    |

| WL                                      | word lattice                                                                                                                                                        |

| WSJ                                     | Wall Street Journal [60]                                                                                                                                            |

|                                         |                                                                                                                                                                     |

| XML                                     | eXtensible Markup Language                                                                                                                                          |

### Chapter 1

### Introduction

### **1.1 Motivation**

As of this writing, speech interfaces are commonly used for search and personal assistants on smartphones and PCs. As these interfaces evolve to offer a more natural user experience, people will become more comfortable interacting with machines by talking with them. The applications of speech interfaces will diversify and include a wider range of devices, such as wearables, appliances, and robots.

A hands-free speech interface consists of a wake-up mechanism, speech-to-text (recognizer), text-based dialogue processor, and text-to-speech (synthesizer). Dialogue processing could include natural language understanding and generation, or translation from a source language to a target language. The components examined by this thesis will frequently be referred to by their acronyms: voice activity detector (VAD) and automatic speech recognizer (ASR).

A VAD classifies an audio stream as speech or non-speech, labeling the start and end time of each speech segment. This is harder than it sounds: in real-world scenarios there can be loud or non-stationary background noise that is difficult to discriminate from speech with any simple algorithm. Some VAD algorithms use expertly tailored criteria based on the energy or spectral content of the signal, and others rely on supervised machine learning to classify feature vectors derived from the signal. It is especially important to optimize the power consumption of the VAD since it must be running at all times.

An ASR transcribes an audio stream into a sequence of words. ASR is usually expressed as a hidden Markov model (HMM) inference problem, where the hidden variables are states within a Markov process modeling speech production, and the observed variables are acoustic features. Transcribing (decoding) an utterance is equivalent to maximum a posteriori (MAP) inference over the HMM, for which we use the Viterbi algorithm. Statistical models are used to evaluate the transition probabilities between (discrete) states and the observation likelihoods over (continuous) features. Over the years, people have developed and refined the ability to train the necessary models from large corpora of transcribed audio files. This training task can be performed offline using a compute cluster. The decoding task is run in real-time for each client device.

Real-time ASR decoding is computationally demanding. The exact workload depends on the task, but most devices supporting speech recognition either have high compute power (like a multicore x86 processor) or an Internet connection linking them to cloud servers. The computational requirements often increase as researchers identify improved modeling techniques. In order to bring speech interfaces to devices that are smaller and cheaper than PCs, or those that lack Internet connections, we need specialized hardware.

As others have shown [47], circuit designs tailored to specific tasks eliminate the overhead of generalpurpose architectures such as x86 or ARM, reducing the energy cost of those tasks by 100x or more. There are also opportunities to modify algorithms and runtime parameters for favorable power/performance tradeoffs. However, there is a big difference in convenience and energy cost between on-chip (small) and off-chip (large) memory that must be taken into account. Software designers typically work with a single flat address space and multi-GB/s bandwidth, relying on caching mechanisms provided by the processor. Porting algorithms to hardware without changing these assumptions does result in some efficiency gains, but shifts the bottleneck from processor to memory. Accommodating memory limitations is a recurring theme in low-power digital design, and ASR is no exception.

Another benefit of adding ASR capabilities to client devices is reduced latency. In dialogue systems, the application needs to react quickly to what the user is saying (as well as emotional or visual cues). Eliminating the roundtrip network latency from the device to a cloud-based recognizer can provide an improvement to the user experience, regardless of power consumption.<sup>1</sup>

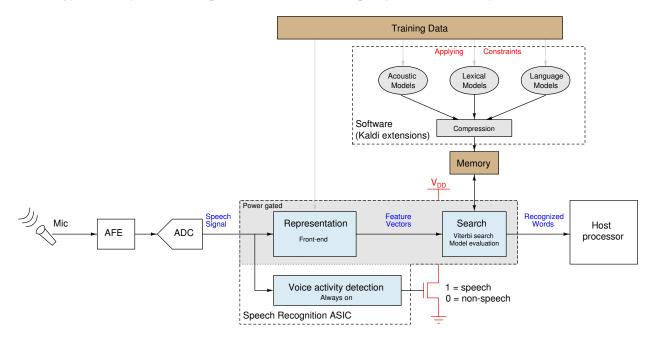

### 1.2 Scope

We are developing a local speech recognition capability for embedded systems, as shown in Figure 1-1. A system designer needs to prioritize and optimize the power consumption of all components jointly. The scope of this thesis is the signal processing IC, designed with awareness of the external memory, and the infrastructure needed to port existing software recognizers to this platform. This memory and its I/O signaling can easily consume more power than the speech recognizer itself. Since speech interfaces are used infrequently (low duty cycle), the memory must be non-volatile. Flash and other non-volatile memories

<sup>&</sup>lt;sup>1</sup>Ramon Prieto (Jibo), personal communication, Jan. 17, 2016.

have a higher energy-per-bit than DRAM, so there is a strong incentive to minimize memory bandwidth. The most affordable and widely used non-volatile memory is NAND flash. According to [27], normalized read energy is typically in the range of 50 pJ/bit for the single-level cell (SLC) variant of NAND flash and 100 pJ/bit (or 8 mW at 10 MB/s) for the more common multilevel cell (MLC) variant. It is worth improving the energy efficiency of the ASR processor until it reaches parity with the memory.

Figure 1-1: Power gated speech recognizer concept. The scope of the work includes the software and circuit components within the dashed boxes.

This thesis explores the idea of using the VAD decision output to power gate the ASR. Otherwise, the ASR would require an explicit wake-up command from the user (i.e., a "push to talk" button), or it would operate continuously and waste power during non-speech input. We will show that using a more sophisticated VAD algorithm (and hence a larger, higher-power VAD circuit) results in the lowest time-averaged system power by reducing false alarms that wake up the more power-hungry ASR and memory.

The rest of this thesis demonstrates digital IC implementations of a VAD and an ASR, and explains the design decisions that make the implementation feasible and minimize system power consumption. Many degrees of freedom and their impacts are considered in pursuit of more accurate, programmable, and scalable ASR capabilities:

• Accuracy is measured as the word error rate (WER) of the transcription result for a particular speech recognition task. This depends on both training and decoding techniques. We demonstrate a controlled loss of accuracy relative to state-of-the-art software speech recognizers across a variety of tasks.

- **Programmability** is the ability to execute different speech recognition tasks (e.g., different vocabularies, topics, speakers, and languages) by using different models and front-end representations. We allow a variety of models trained using the open-source Kaldi tools [64] to be converted into formats supported by the chip.

- Scalability is the ability to adjust the chip's speed and power consumption according to the needs of the speech recognition task (or a power budget). We demonstrate scalability at several levels: selecting models of appropriate complexity, adjusting runtime decoding parameters, and adjusting circuit voltages and clock frequencies.

This research resulted in the fabrication of three IC chips, summarized in Figure 1-2. The process has been cumulative, with the third chip integrating and refining (or replacing) structures developed in the other two:

- The first chip provides a proof of concept for low-power ASR and serves as a baseline for the remainder of our work. The chip was fabricated using a 65 nm process; it measures 2.5 × 2.5 mm, and is programmable with industry-standard WFST and GMM speech models. This chip performs a 5,000 word recognition task in real-time with 13.0% word error rate, 6.0 mW core power consumption, and a search efficiency of approximately 16 nJ per hypothesis. This work is described in [66] and [67].

- The second chip was used to evaluate VAD algorithms within our system power model, considering both the power and accuracy of the VAD. This chip is operational, but we are withholding further measurement results due to a functional bug in one of the three algorithms.

- The third chip implements many enhancements to the baseline ASR design and allows the ASR to be power gated by decisions from an onboard VAD.

To simplify the discussion, we describe only the third chip in this thesis.

### **1.3 ASR formulation**

A short summary of the ASR problem will help you understand the acoustic modeling and search techniques described in later chapters.

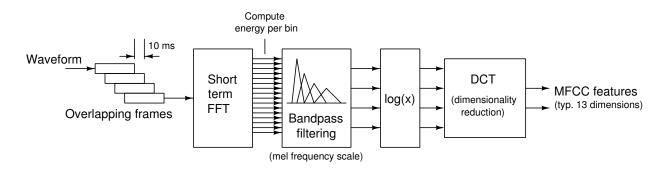

The ASR system has a front-end which transforms audio (e.g., 16-bit samples at 8 kHz or 16 kHz) into a lower-rate, higher-dimensional feature representation. We typically use 13-dimensional mel-frequency cepstral coefficient (MFCC) features [20] based on 25 ms frames of audio, with a 10 ms interval between frames. The MFCC features can be augmented with log-energy, time derivatives (e.g., deltas or doubledeltas), and/or temporal context (features from previous frames) to improve performance. A typical utter-

|                | ASR v1                                                                                                                                                     | VAD                                                                                                                                                                  | ASR v2 + VAD                                                                                                                                      |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                |                                                                                                                                                            |                                                                                                                                                                      |                                                                                                                                                   |  |

| Dimensions     | $2.5 \times 2.5 \text{ mm}$                                                                                                                                | $1.84 \times 1.84 \text{ mm}$                                                                                                                                        | $3.63 \times 3.63 \text{ mm}$                                                                                                                     |  |

| Logic (kgates) | 340                                                                                                                                                        | 472                                                                                                                                                                  | 2088                                                                                                                                              |  |

| Memory (kb)    | 2400                                                                                                                                                       | 660                                                                                                                                                                  | 5840                                                                                                                                              |  |

| Clock freq.    | 20–110 MHz                                                                                                                                                 | 0.6–2.0 MHz                                                                                                                                                          | 1.5–85 MHz                                                                                                                                        |  |

| Description    | <ul> <li>WFST/GMM models</li> <li>No training infrastructure;<br/>downloaded HTK models</li> <li>Tested on WSJ eval92-5k:<br/>13.0% WER, 6.0 mW</li> </ul> | <ul> <li>Choice of 3 algorithms for power/accuracy tradeoff</li> <li>SPI and I<sup>2</sup>S interfaces</li> <li>3–18 μW at supply voltages down to 0.49 V</li> </ul> | <ul> <li>WFST/DNN models</li> <li>Models can be generated from Kaldi recognizer</li> <li>Multiple power domains, off-chip power gating</li> </ul> |  |

Figure 1-2: Progression of research program through three IC tapeouts.

ance (e.g., sentence) lasts 1–10 seconds, or 100–1,000 frames. These feature vectors are handed off to the HMM.

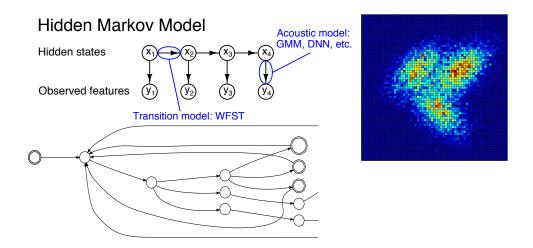

The HMM is a graphical model expressing a relationship between hidden variables  $x_t$  and observed variables  $y_t$ . The regular structure of connections in this graph (Markov property) is exploited to allow approximate inference in linear time (Viterbi algorithm), making statistical speech recognition tractable.

Figure 1-3 is a high-level illustration of a speech HMM. The HMM uses knowledge of the underlying speech production process to model hidden state sequences  $x_t$ . To perform ASR we supply MFCC feature vectors for  $y_t$  and use the HMM to estimate the most likely values of  $x_t$ .

Using the HMM framework requires modeling the dependencies between variables, specifically the transition model  $p(x_{t+1}|x_t)$  and the emission model  $p(y_t|x_t)$ . The transition model incorporates information about the language, including its vocabulary and grammatical constraints; the hidden states  $x_t$  are discrete variables. The emission model describes how observations  $y_t$  vary depending on the unobserved state  $x_t$ ; in speech recognition, this is called the acoustic model. These observations reflect the speech signal generated by the speaker's vocal tract, and the influence of the channel (the microphone and the acoustic environment).

Properly accounting for multiple levels of knowledge (e.g., context, pronunciation, and grammar) in the transition model compounded the complexity of early HMM decoders. The weighted finite-state transducer (WFST) is a state machine representation that allows each component to be described separately [54, 55] and

Figure 1-3: HMM formulation of ASR. Separate frameworks are used to evaluate the transition probabilities  $p(x_{t+1}|x_t)$  (bottom) and observation probabilities  $p(y_t|x_t)$  (right).

then composed into a single WFST encompassing the entire search space [1]. (Section 3.2.3 specifies these components more precisely.) The WFST can be viewed as a graph that is easily queried for the (sparse) transition probabilities  $p(x_{t+1}|x_t)$ , which convey the constraints of the language model and lexicon. All possible transitions between states are expressed as weighted, labeled arcs. A WFST-based decoder can complete tasks of varying complexity in different domains and languages by substituting the appropriate model parameters.

The HMM factorizes the joint probability of all observed and hidden variables as:

$$p(x,y) = p(x_0) \prod_{t=0}^{T-1} p(x_{t+1}|x_t) p(y_t|x_t)$$

In this formulation,  $x_t$  is a discrete variable referring to a state in a weighted finite-state transducer (WFST) [55];  $y_t$  is a real-valued vector. The hidden state sequence  $\mathbf{X} = \{x_0, x_1, \dots, x_{T-1}\}$  specifies a word sequence  $\mathbf{W}$  via the output labels of WFST arcs traversed by  $\mathbf{X}$ . Finding the most likely word sequence given a set of observations  $\mathbf{Y}$  is MAP inference:  $\mathbf{W}^* = \arg \max_{\mathbf{W}} p(\mathbf{W}|\mathbf{Y})$ . We perform MAP inference over states and then convert the result to words.

To estimate the state sequence from features, we use the Viterbi search algorithm. The algorithm maintains a list of hypotheses, or active states, at each time step. This search procedure is described in [39] and many other sources. An important step in Viterbi search is the forward update, which approximates the likelihood of all reachable states at the next time step:

$$p(x_{t+1}) = \sum_{x_t} p(x_t) p(x_{t+1}|x_t) p(y_{t+1}|x_{t+1})$$

$$\approx \max_{x_t} p(x_t) p(x_{t+1}|x_t) p(y_{t+1}|x_{t+1})$$

In our implementations, the existing state likelihood  $p(x_t)$  is retrieved from an "active state list" in local memory. The transition probability  $p(x_{t+1}|x_t)$  is the weight of the WFST arc[s] leading from state  $x_t$  to state  $x_{t+1}$ . The emission probability  $p(y_{t+1}|x_{t+1})$  is an acoustic likelihood specified by the acoustic model.

There are many possible values for  $x_t$  because WFSTs for ASR typically have millions of states. To speed up decoding, ASR systems use a "beam search" variant of the Viterbi algorithm that discards unlikely hypotheses.<sup>2</sup> There are several possible criteria for saving hypotheses; for example, you could discard every hypothesis whose log-likelihood falls below a certain cutoff. In this scheme, the difference between the cutoff and the maximum log-likelihood is called the beam width. Decreasing (narrowing) the beam width saves computation time and introduces search errors.

The acoustic model describes the expected probability distribution of feature vectors, given a particular state  $x_t$ . Rather than using a separate distribution for each state in the WFST, the states are grouped into clusters (typically 1,000 to 10,000) called "tied states" or "senones." This clustering is usually performed in a top-down fashion [92]. All states in each cluster share one probability density. Evaluating transition probabilities (from the WFST) and acoustic model likelihoods requires fetching model parameters from a large external memory.

Rather than designing one universal ASR model, we follow the standard practice of training different recognizers for different tasks. Some of the tasks we studied are listed in Table 1.1.

| Name                 | Size (hr) | Vocabulary (approx.) | Channel   | Speech type | LM Perplexity |

|----------------------|-----------|----------------------|-----------|-------------|---------------|

| TIDIGITS [45]        | 4.1       | 11                   | Telephone | Read        | 10.8          |

| Jupiter [96]         | 73        | 2k                   | Telephone | Spontaneous | 8.58          |

| Nutrition [43]       | 2.7       | 7k                   | Wideband  | Read        | 23.7          |

| WSJ [60] (eval92-5k) | 81        | 5k                   | Wideband  | Read        | 65.6          |

| WSJ [60] (dev93)     | 81        | 20k+                 | Wideband  | Read        | 166           |

Table 1.1: Datasets used for ASR experiments.

Each task is based on a corpus of training and test data, and has its own (possibly domain-specific) vocabulary and acoustic properties. All tasks rely on N-gram language models, or LMs [26], ranging from

<sup>&</sup>lt;sup>2</sup>There are usually diminishing returns to tracking more than a few thousand hypotheses, but this depends on the task.

unigram (TIDIGITS) to 4-gram (Jupiter). To convey the search complexity of each task, we specify the LM perplexity [37]; this can be interpreted as a branching factor, with higher perplexity indicating fewer constraints for search. (The perplexity of the TIDIGITS model is close to 11, since at any point in the search there are 11 possible words which are almost equally likely.<sup>3</sup>) Having a range of tasks lets us evaluate the scalability of the ASR implementation.

### **1.4 Prior art**

Since the late 1980s, there have been sporadic efforts to exploit special-purpose hardware for speech applications. Application-specific integrated circuits (ASICs) for HMM-based speech recognition were reported as early as 1991 [80], followed by power-conscious implementations intended for portable devices [12]. The "In Silico Vox" project [48] created sophisticated hardware ports of Sphinx-3, a well-established software framework for ASR. Between 2006 and 2010 this project developed several hardware decoders on both single-FPGA and multi-FPGA platforms [49, 46, 11], achieving 10x faster than real-time performance on a Wall Street Journal (WSJ) task. These researchers had a broad focus on making hardware ASR work and scaling to larger tasks and lower power.

More specialized research efforts have examined changes in ASR algorithms and their applicability to hardware. One area of evolution has been in the use of WFSTs, which are a key component of the modern ASR framework. WFSTs are now commonplace in software speech recognizers, including commercial systems [72]. Perhaps due to long development cycles, most of the hardware implementations realized so far are based on non-WFST software decoders. Digital circuits using WFSTs were presented in 2008 [16], contributing an important observation that pre-processing the WFST could eliminate the need to consider unlabeled arcs recursively during each frame. Taking advantage of external DRAM memory with 3.2 GB/s bandwidth, [90] illustrated how to split the decoder's active state list between internal and external memory to achieve better accuracy with limited internal SRAM.

Another focus area in ASR research has been acoustic modeling. All hardware ASR implementations we know of have used Gaussian mixture models (GMMs) with varying levels of complexity (number of tied states and number of Gaussian components per distribution). To speed up computation, designers have performed frame skipping and Gaussian selection [61] and used fixed-point parameters [9]. Meanwhile, deep neural networks (DNNs) and other neural network architectures have become popular for ASR due to their improved accuracy [34]. The circuits community has studied DNNs and developed efficient implementa-

<sup>&</sup>lt;sup>3</sup>TIDIGITS uses the ten digits (zero through nine), but zero can be spoken as "oh;" this is treated as an 11th word.

tions, primarily for computer vision [15, 59].

Other recent work performed architectural exploration: choosing how to divide hardware resources between acoustic modeling and search, and two-pass decoding with the first pass performed by hardware [7]. Code generation tools can help rapidly evaluate different accelerator kernels specified in a high-level language [78]. Acoustic models generally see large efficiency gains from acceleration, and front-ends generally do not, but there is no consensus on the proper hardware/software partitioning for search–this seems to depend on the application.

The wide range of algorithms available for VAD also provides opportunities to apply special-purpose architectures. Power can be minimized through a variety of techniques, whether minimum-energy operation in deeply scaled CMOS [71], or mixed-signal design with adaptive feature granularity [5]. These efforts have brought VAD power consumption down to a few  $\mu$ W.

Contemporary efforts in ASR have continued expanding decoder capabilities for general-purpose transcription applications with a 60,000 word (or larger) vocabulary. For example, [41] proposed an architecture for achieving much higher throughput (127x faster than real-time) using an ASIC. Another effort [31, 30, 29] bridged the gap between high-performance and low-power applications, applying a series of optimizations to a Japanese-language system called Julius in order to obtain just 54 mW of power consumption and 82 MB/s of memory bandwidth during real-time decoding. Also, indepdendently of this work, [3] discussed techniques of WFST pruning and search that are relevant to low-power ASR applications.

Throughout this thesis we will cite additional prior work relating to each aspect of ASR/VAD design.

### **1.5** Contributions

This thesis builds on previous efforts in two major areas: (1) circuit implementations supporting modern algorithms and frameworks; and (2) pushing down power consumption from a system-level perspective.

Adopting modern algorithms: While DNNs have been used in ASR for several years, this work may be the first realization of a hardware speech recognizer using DNNs. This revision is justified by our comparison of DNNs with two other types of acoustic models: GMMs and subspace GMMs.

Our work in [67] was to our knowledge the first ASIC speech decoder to support WFSTs, and the first to handle the entire speech recognition chain from audio to text. In this thesis, continued studies of HMM search and its demands on the WFST data structure lead to a revised architecture with WFST compression and a new caching strategy.

While WFSTs and DNNs are fairly generic, there are many variants to how they are constructed and used. We made our decoder compatible with Kaldi [64], a popular open-source library for speech recognition. This simplifies the process of deploying a recognizer on our hardware platform. We designed auxiliary hardware and software components to make this possible.

Algorithms used in IC implementations of VAD have also lagged behind software implementations. We demonstrate hardware implementations of three VAD algorithms adapted from recent literature.

**System-level power reductions:** We want to minimize the size and power of a speech-enabled system, as opposed to a single component (such as the core logic of an ASR chip). Modeling the power consumption of all relevant components led us to realize that external (off-chip) memory is a major bottleneck. Reducing the bandwidth expected of this memory is our top priority, dictating many of the design choices we made. The end result is that many ASR tasks can be run with less than 10 MB/s of bandwidth, comfortably within the limits of a single NAND flash die. This is significantly lower than the bandwidth targets of previous work. For comparison, [17] (which describes in-depth techniques for optimizing memory access) reports bandwidth of 219 MB/s. Our bandwidth reductions come from several sources that will be discussed in more detail below. We believe that the core area and power tradeoffs made to achieve these reductions are acceptable, especially since they are mitigated by CMOS scaling.

VAD is an important part of our system power reduction strategy. We provide a simple model for power consumption when VAD is used to power gate an ASR, and show how this guides the selection of VAD algorithms. Our VAD is designed to operate without any external memory, which is necessary to achieve  $\mu$ W power levels in the inactive state.

Wherever possible, we use low-power IC design techniques including clock gating, variation-aware timing constraints, and multiple power domains.

### **1.6 Guide to chapters**

The remaining chapters describe the design of our ASR/VAD system in a holistic fashion, integrating the discussion of algorithms and architectures and quantifying the impact of each contribution on our goals of accuracy, programmability, and scalability. Chapters 2 and 3 focus on the largest components of the ASR: acoustic modeling and search. Chapter 4 considers VAD. Chapter 5 discusses software and hardware components that support these components and enable a system demonstration. Chapter 6 discusses the IC implementation process and testing results; Chapter 7 concludes.

### Chapter 2

### **Acoustic modeling**